## SHARP

# LH28F160S5HNS-S1

## Flash Memory 16Mbit (2Mbitx8/1Mbitx16)

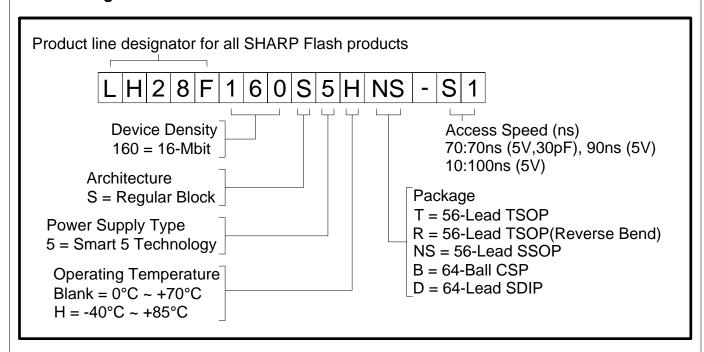

(Model Number: LHF16KS1) *Lead-free (Pb-free)*

Spec. Issue Date: October 8, 2004

Spec No: EL16X079

| SPEC. No. | EL16 | X 0 | 7 9  |

|-----------|------|-----|------|

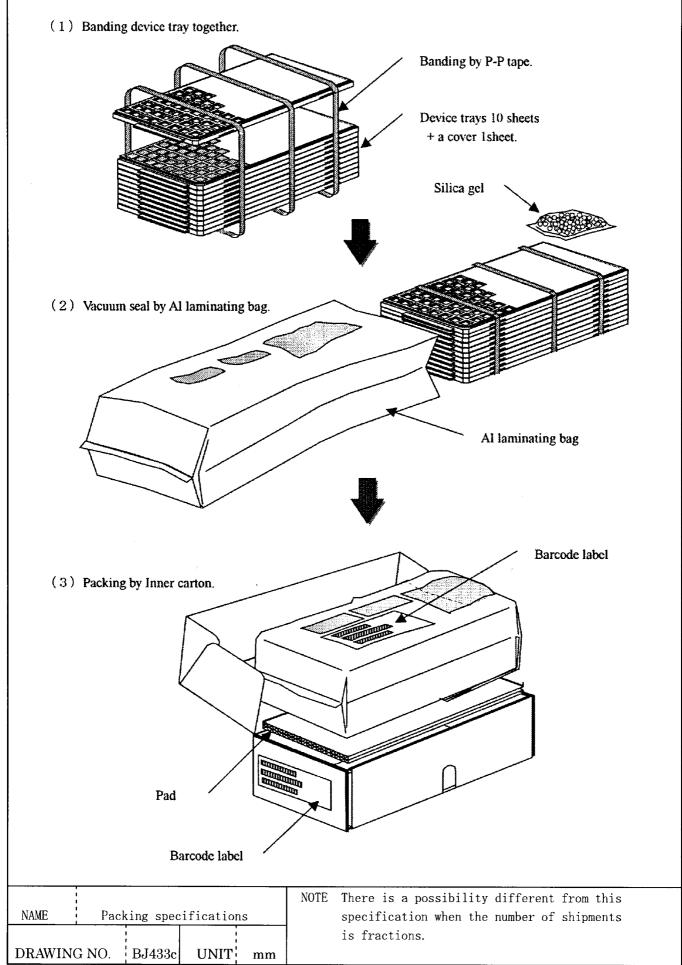

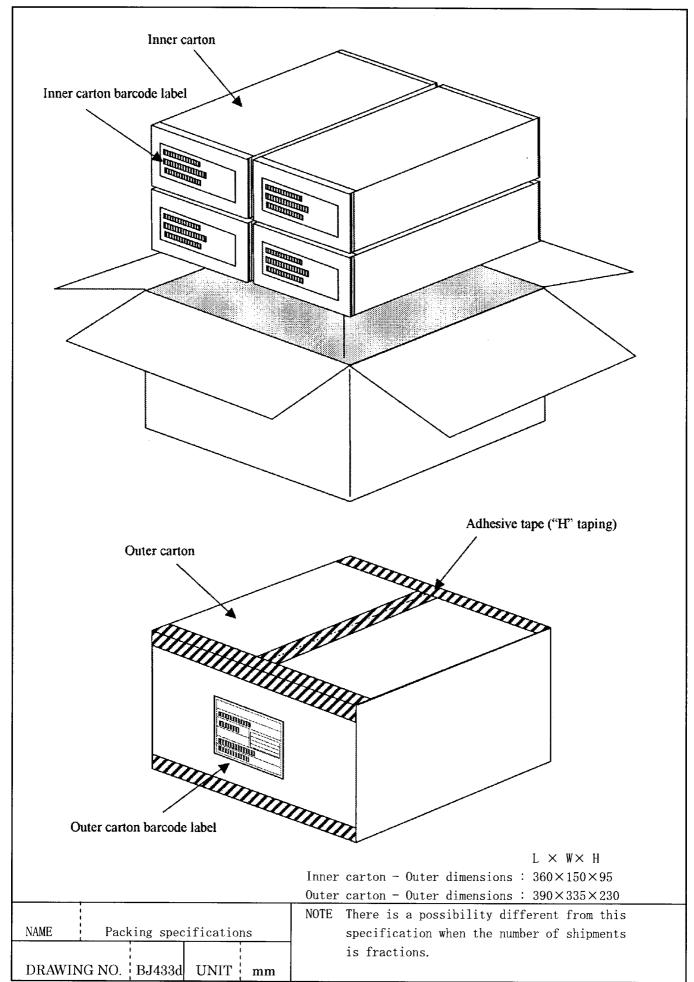

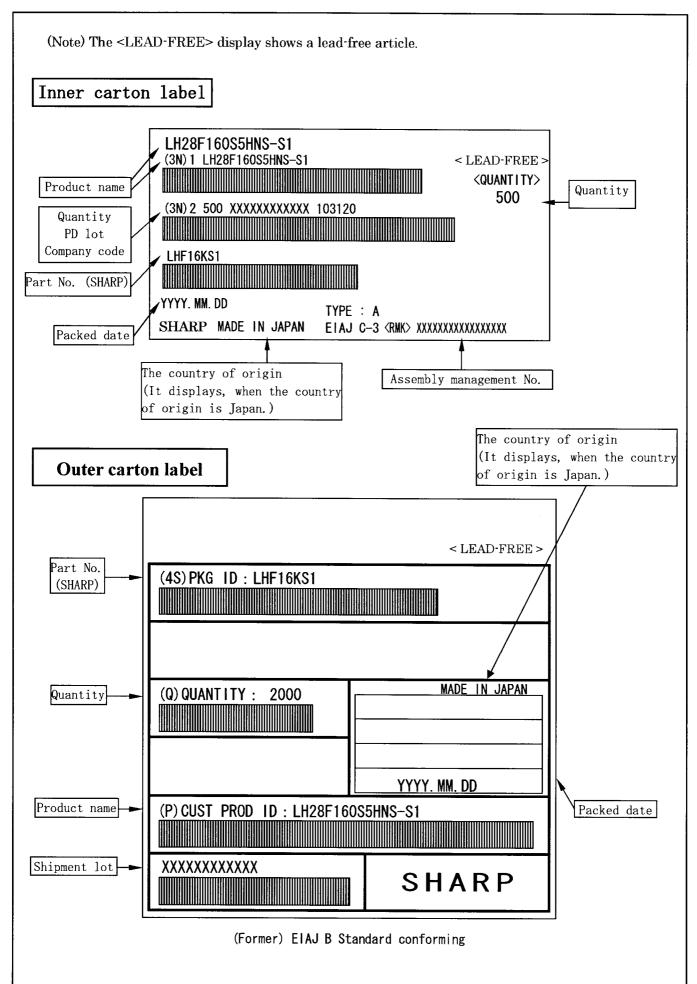

| ISSUE:    | Oct. | 8.  | 2004 |

| То  |   |  |  |  |

|-----|---|--|--|--|

| -1  | • |  |  |  |

| 1 0 | , |  |  |  |

| •                           |                                          |

|-----------------------------|------------------------------------------|

| SPEC                        | IFICATIONS                               |

| Product Type 1 6            | Mbit Flash Memory                        |

| LH28                        | F 1 6 0 S 5 HN S - S 1                   |

| Model No.                   | (LHF16KS1)                               |

| CUSTOMERS ACCEPTANCE  DATE: |                                          |

| BY:                         | PRESENTED                                |

|                             | BY: // / / / / / / / / / / / / / / / / / |

|                             | REVIEWED BY: PREPARED BY:                |

|                             | Product Development Dept. I              |

System-Flash Division Integrated Circuits Group

SHARP CORPORATION

## LHF16KS1

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- •When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- Office electronics

- Instrumentation and measuring equipment

- Machine tools

- Audiovisual equipment

- Home appliance

- •Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- Mainframe computers

- Traffic control systems

- Gas leak detectors and automatic cutoff devices

- •Rescue and security equipment

- •Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- Aerospace equipment

- Communications equipment for trunk lines

- •Control equipment for the nuclear power industry

- •Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

## **CONTENTS**

| PAGE                                            | P                                                       | AGE   |

|-------------------------------------------------|---------------------------------------------------------|-------|

| 1 INTRODUCTION 3                                | 5 DESIGN CONSIDERATIONS                                 | 30    |

| 1.1 Product Overview3                           | 5.1 Three-Line Output Control                           | 30    |

|                                                 | 5.2 STS and Block Erase, Full Chip Erase, (Multi)       |       |

| 2 PRINCIPLES OF OPERATION6                      | Word/Byte Write and Block Lock-Bit Configura            | ation |

| 2.1 Data Protection7                            | Polling                                                 | 30    |

|                                                 | 5.3 Power Supply Decoupling                             | 30    |

| <b>3 BUS OPERATION</b>                          | 5.4 V <sub>PP</sub> Trace on Printed Circuit Boards     | 30    |

| 3.1 Read 7                                      | 5.5 V <sub>CC</sub> , V <sub>PP</sub> , RP# Transitions | 31    |

| 3.2 Output Disable 7                            | 5.6 Power-Up/Down Protection                            | 31    |

| 3.3 Standby7                                    | 5.7 Power Dissipation                                   | 31    |

| 3.4 Deep Power-Down7                            |                                                         |       |

| 3.5 Read Identifier Codes Operation 8           | 6 ELECTRICAL SPECIFICATIONS                             | 32    |

| 3.6 Query Operation 8                           | 6.1 Absolute Maximum Ratings                            | 32    |

| 3.7 Write8                                      | 6.2 Operating Conditions                                | 32    |

|                                                 | 6.2.1 Capacitance                                       | 32    |

| 4 COMMAND DEFINITIONS 8                         | 6.2.2 AC Input/Output Test Conditions                   | 33    |

| 4.1 Read Array Command11                        | 6.2.3 DC Characteristics                                | 34    |

| 4.2 Read Identifier Codes Command               | 6.2.4 AC Characteristics - Read-Only Operations         | s .36 |

| 4.3 Read Status Register Command11              | 6.2.5 AC Characteristics - Write Operations             | 39    |

| 4.4 Clear Status Register Command11             | 6.2.6 Alternative CE#-Controlled Writes                 | 41    |

| 4.5 Query Command12                             | 6.2.7 Reset Operations                                  | 43    |

| 4.5.1 Block Status Register 12                  | 6.2.8 Block Erase, Full Chip Erase, (Multi)             |       |

| 4.5.2 CFI Query Identification String           | Word/Byte Write and Block Lock-Bit                      |       |

| 4.5.3 System Interface Information              | Configuration Performance                               | 44    |

| 4.5.4 Device Geometry Definition                |                                                         |       |

| 4.5.5 SCS OEM Specific Extended Query Table 14  | 7 ADDITIONAL INFORMATION                                |       |

| 4.6 Block Erase Command                         | 7.1 Ordering Information                                | 45    |

| 4.7 Full Chip Erase Command                     |                                                         |       |

| 4.8 Word/Byte Write Command                     | 8 PACKAGE AND PACKING SPECIFICATION                     | 46    |

| 4.9 Multi Word/Byte Write Command               |                                                         |       |

| 4.10 Block Erase Suspend Command                |                                                         |       |

| 4.11 (Multi) Word/Byte Write Suspend Command 17 |                                                         |       |

| 4.12 Set Block Lock-Bit Command                 |                                                         |       |

| 4.13 Clear Block Lock-Bits Command              |                                                         |       |

| 4.14 STS Configuration Command                  |                                                         |       |

|                                                 |                                                         |       |

## LH28F160S5HNS-S1 16M-BIT (2MBx8/1MBx16) Smart 5 Flash MEMORY

- Smart 5 Technology

- 5V V<sub>CC</sub>

- 5V V<sub>PP</sub>

- Common Flash Interface (CFI)

- Universal & Upgradable Interface

- Scalable Command Set (SCS)

- **■** High Speed Write Performance

- 32 Bytes x 2 plane Page Buffer

- 2µs/Byte Write Transfer Rate

- **■** High Speed Read Performance

- 70ns(5V±0.25V), 90ns(5V±0.5V)

- Operating Temperature

- -40°C to +85°C

- **■** Enhanced Automated Suspend Options

- Write Suspend to Read

- Block Erase Suspend to Write

- Block Erase Suspend to Read

- High-Density Symmetrically-Blocked Architecture

- Thirty-two 64K-byte Erasable Blocks

- SRAM-Compatible Write Interface

- User-Configurable x8 or x16 Operation

- Enhanced Data Protection Features

- Absolute Protection with V<sub>PP</sub>=GND

- Flexible Block Locking

- Erase/Write Lockout during Power Transitions

- **■** Extended Cycling Capability

- 100,000 Block Erase Cycles

- 3.2 Million Block Erase Cycles/Chip

- **■** Low Power Management

- Deep Power-Down Mode

- Automatic Power Savings Mode

Decreases I<sub>CC</sub> in Static Mode

- Automated Write and Erase

- Command User Interface

- Status Register

- Industry-Standard Packaging

- 56-Lead SSOP

- ETOX<sup>TM\*</sup> V Nonvolatile Flash Technology

- CMOS Process (P-type silicon substrate)

- Not designed or rated as radiation hardened

SHARP's LH28F160S5HNS-S1 Flash memory with Smart 5 technology is a high-density, low-cost, nonvolatile, read/write storage solution for a wide range of applications. Its symmetrically-blocked architecture, flexible voltage and extended cycling provide for highly flexible component suitable for resident flash arrays, SIMMs and memory cards. Its enhanced suspend capabilities provide for an ideal solution for code + data storage applications. For secure code storage applications, such as networking, where code is either directly executed out of flash or downloaded to DRAM, the LH28F160S5HNS-S1 offers three levels of protection: absolute protection with  $V_{\rm PP}$  at GND, selective hardware block locking, or flexible software block locking. These alternatives give designers ultimate control of their code security needs.

The LH28F160S5HNS-S1 is conformed to the flash Scalable Command Set (SCS) and the Common Flash Interface (CFI) specification which enable universal and upgradable interface, enable the highest system/device data transfer rates and minimize device and system-level implementation costs.

The LH28F160S5HNS-S1 is manufactured on SHARP's  $0.35\mu m$  ETOX<sup>TM\*</sup> V process technology. It come in industry-standard package: the 56-Lead SSOP, ideal for board constrained applications.

\*ETOX is a trademark of Intel Corporation.

## 1 INTRODUCTION

This datasheet contains LH28F160S5HNS-S1 specifications. Section 1 provides a flash memory overview. Sections 2, 3, 4, and 5 describe the memory organization and functionality. Section 6 covers electrical specifications.

#### 1.1 Product Overview

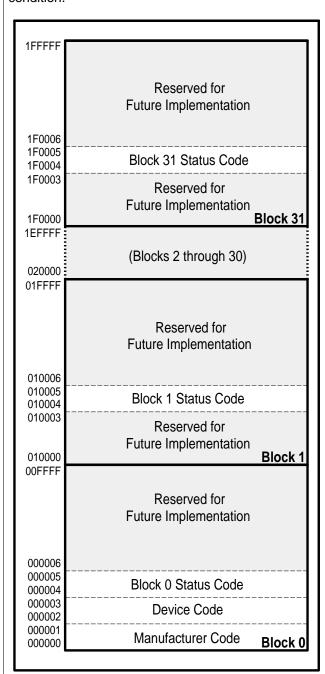

The LH28F160S5HNS-S1 is a high-performance 16M-bit Smart 5 Flash memory organized as 2MBx8/1MBx16. The 2MB of data is arranged in thirty-two 64K-byte blocks which are individually erasable, lockable, and unlockable in-system. The memory map is shown in Figure 3.

Smart 5 technology provides a choice of  $V_{CC}$  and  $V_{PP}$  combinations, as shown in Table 1, to meet system performance and power expectations. 5V  $V_{CC}$  provides the highest read performance.  $V_{PP}$  at 5V eliminates the need for a separate 12V converter, while  $V_{PP}$ =5V maximizes erase and write performance. In addition to flexible erase and program voltages, the dedicated  $V_{PP}$  pin gives complete data protection when  $V_{PP} \le V_{PPL K}$ .

Table 1. V<sub>CC</sub> and V<sub>PP</sub> Voltage Combinations Offered by Smart 5 Technology

| V <sub>CC</sub> Voltage | V <sub>PP</sub> Voltage |

|-------------------------|-------------------------|

| 5V                      | 5V                      |

Internal  $V_{CC}$  and  $V_{PP}$  detection Circuitry automatically configures the device for optimized read and write operations.

A Command User Interface (CUI) serves as the interface between the system processor and internal operation of the device. A valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase, full chip erase, (multi) word/byte write and block lock-bit configuration operations.

A block erase operation erases one of the device's 64K-byte blocks typically within 0.34s (5V  $V_{CC}$ , 5V  $V_{PP}$ ) independent of other blocks. Each block can be independently erased 100,000 times (3.2 million block erases per device). Block erase suspend mode allows system software to suspend block erase to read or write data from any other block.

A word/byte write is performed in byte increments typically within 9.24µs (5V  $V_{CC}$ , 5V  $V_{PP}$ ). A multi word/byte write has high speed write performance of 2µs/byte (5V  $V_{CC}$ , 5V  $V_{PP}$ ). (Multi) Word/byte write suspend mode enables the system to read data or

execute code from any other flash memory array location.

Individual block locking uses a combination of bits and WP#, Thirty-two block lock-bits, to lock and unlock blocks. Block lock-bits gate block erase, full chip erase and (multi) word/byte write operations. Block lock-bit configuration operations (Set Block Lock-Bit and Clear Block Lock-Bits commands) set and cleared block lock-bits.

The status register indicates when the WSM's block erase, full chip erase, (multi) word/byte write or block lock-bit configuration operation is finished.

The STS output gives an additional indicator of WSM activity by providing both a hardware signal of status (versus software polling) and status masking (interrupt masking for background block erase, for example). Status polling using STS minimizes both CPU overhead and system power consumption. STS pin can be configured to different states using the Configuration command. The STS pin defaults to RY/BY# operation. When low, STS indicates that the WSM is performing a block erase, full chip erase, (multi) word/byte write or block lock-bit configuration. STS-High Z indicates that the WSM is ready for a new command, block erase is suspended and (multi) word/byte write are inactive, (multi) word/byte write are suspended, or the device is in deep power-down mode. The other 3 alternate configurations are all pulse mode for use as a system interrupt.

The access time is 70ns ( $t_{AVQV}$ ) over the extended temperature range (-40°C to +85°C) and  $V_{CC}$  supply voltage range of 4.75V-5.25V. At lower  $V_{CC}$  voltage, the access time is 90ns (4.5V-5.5V).

The Automatic Power Savings (APS) feature substantially reduces active current when the device is in static mode (addresses not switching). In APS mode, the typical  $I_{CCR}$  current is 1 mA at 5V  $V_{CC}$ .

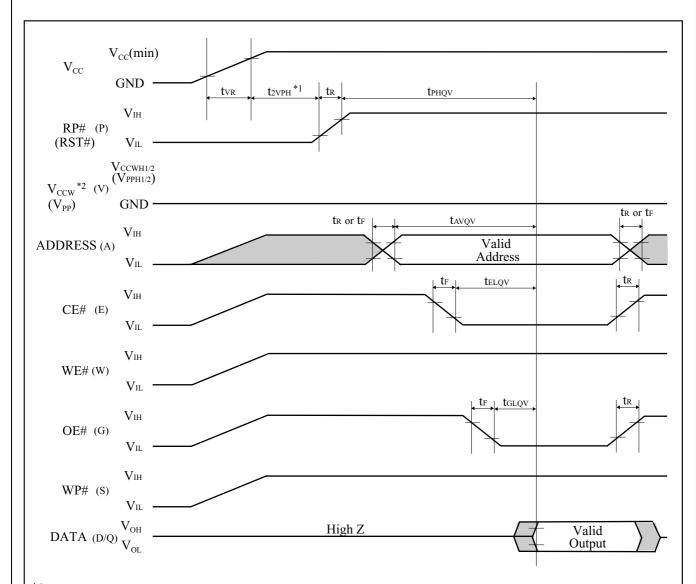

When either  $CE_0^{\dagger}$  or  $CE_1^{\dagger}$ , and RP# pins are at  $V_{CC}$ , the  $I_{CC}$  CMOS standby mode is enabled. When the RP# pin is at GND, deep power-down mode is enabled which minimizes power consumption and provides write protection during reset. A reset time  $(t_{PHQV})$  is required from RP# switching high until outputs are valid. Likewise, the device has a wake time  $(t_{PHEL})$  from RP#-high until writes to the CUI are recognized. With RP# at GND, the WSM is reset and the status register is cleared.

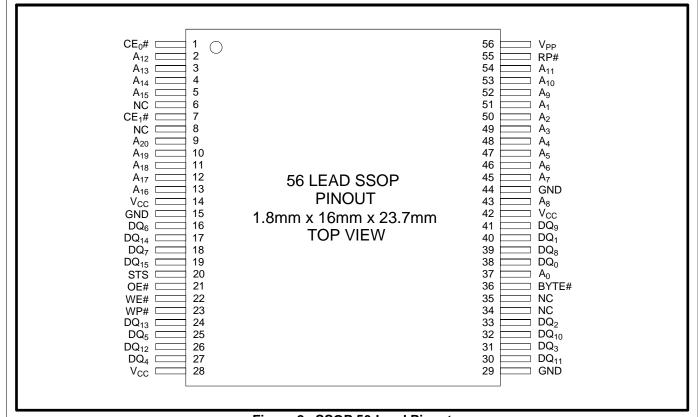

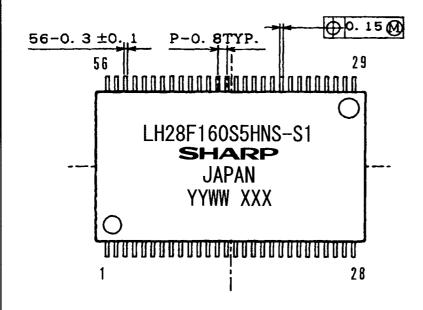

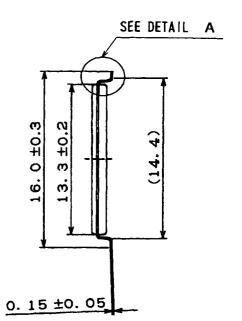

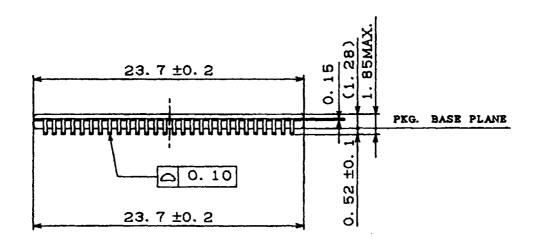

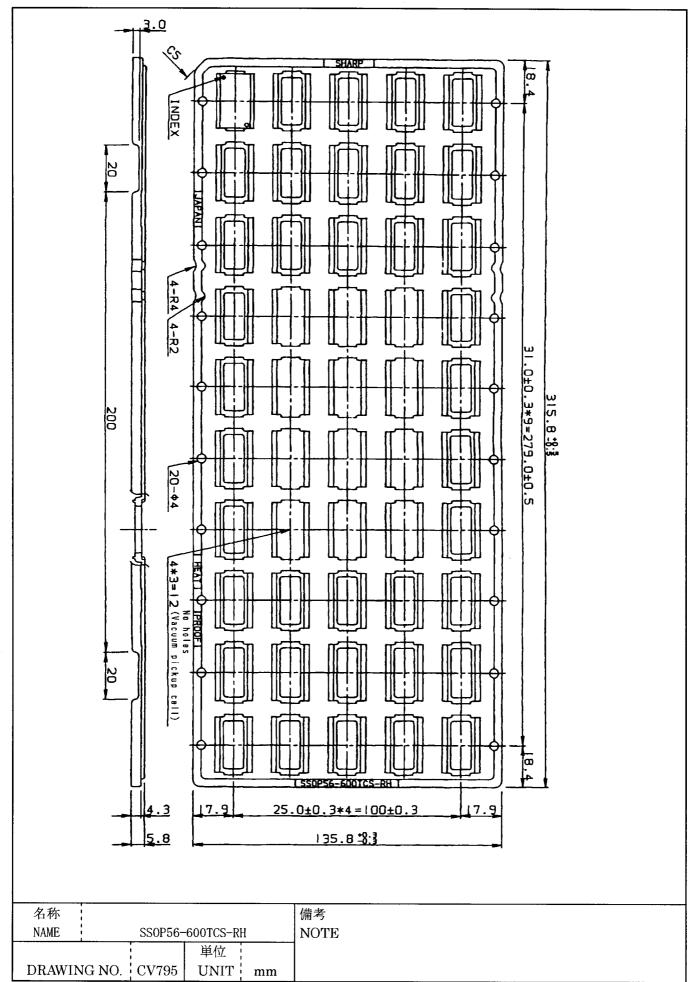

The device is available in 56-Lead SSOP (Shrink Small Outline Package). Pinout is shown in Figure 2.

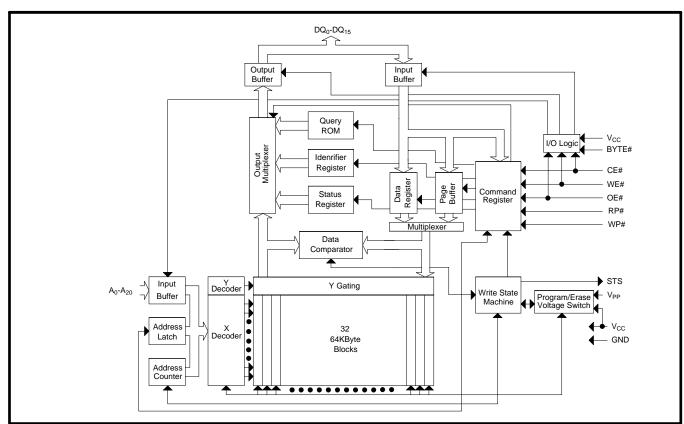

Figure 1. Block Diagram

Figure 2. SSOP 56-Lead Pinout

|                                         |                         | Table 2. Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                  | Type                    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A <sub>0</sub> -A <sub>20</sub>         | INPUT                   | ADDRESS INPUTS: Inputs for addresses during read and write operations. Addresses are internally latched during a write cycle.  Ao: Byte Select Address. Not used in x16 mode(can be floated).  A1-A4: Column Address. Selects 1 of 16 bit lines.  A5-A15: Row Address. Selects 1 of 2048 word lines.  A16-A20: Block Address.                                                                                                                                                                                                                                                                                                                                                                                                              |

| DQ <sub>0</sub> -DQ <sub>15</sub>       | INPUT/<br>OUTPUT        | DATA INPUT/OUTPUTS:  DQ <sub>0</sub> -DQ <sub>7</sub> :Inputs data and commands during CUI write cycles; outputs data during memory array, status register, query, and identifier code read cycles. Data pins float to high-impedance when the chip is deselected or outputs are disabled. Data is internally latched during a write cycle.  DQ <sub>8</sub> -DQ <sub>15</sub> :Inputs data during CUI write cycles in x16 mode; outputs data during memory array read cycles in x16 mode; not used for status register, query and identifier code read mode. Data pins float to high-impedance when the chip is deselected, outputs are disabled, or in x8 mode(Byte#=V <sub>IL</sub> ). Data is internally latched during a write cycle. |

| CE <sub>0</sub> #,<br>CE <sub>1</sub> # | INPUT                   | <b>CHIP ENABLE:</b> Activates the device's control logic, input buffers decoders, and sense amplifiers. Either CE <sub>0</sub> # or CE <sub>1</sub> # V <sub>IH</sub> deselects the device and reduces power consumption to standby levels. Both CE <sub>0</sub> # and CE <sub>1</sub> # must be V <sub>II</sub> to select the devices.                                                                                                                                                                                                                                                                                                                                                                                                    |

| RP#                                     | INPUT                   | <b>RESET/DEEP POWER-DOWN:</b> Puts the device in deep power-down mode and resets internal automation. RP# $V_{IH}$ enables normal operation. When driven $V_{IL}$ , RP# inhibits write operations which provides data protection during power transitions. Exit from deep power-down sets the device to read array mode.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OE#                                     | INPUT                   | OUTPUT ENABLE: Gates the device's outputs during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WE#                                     | INPUT                   | WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data are latched on the rising edge of the WE# pulse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| STS                                     | OPEN<br>DRAIN<br>OUTPUT | STS (RY/BY#): Indicates the status of the internal WSM. When configured in level mode (default mode), it acts as a RY/BY# pin. When low, the WSM is performing an internal operation (block erase, full chip erase, (multi) word/byte write or block lock-bit configuration). STS High Z indicates that the WSM is ready for new commands, block erase is suspended, and (multi) word/byte write is inactive, (multi) word/byte write is suspended or the device is in deep power-down mode. For alternate configurations of the STATUS pin, see the Configuration command.                                                                                                                                                                |

| WP#                                     | INPUT                   | <b>WRITE PROTECT:</b> Master control for block locking. When V <sub>IL</sub> , Locked blocks can not be erased and programmed, and block lock-bits can not be set and reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BYTE#                                   | INPUT                   | <b>BYTE ENABLE:</b> BYTE# $V_{IL}$ places device in x8 mode. All data is then input or output on $DQ_{0-7}$ , and $DQ_{8-15}$ float. BYTE# $V_{IH}$ places the device in x16 mode, and turns off the $A_0$ input buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>PP</sub>                         | SUPPLY                  | BLOCK ERASE, FULL CHIP ERASE, (MULTI) WORD/BYTE WRITE, BLOCK LOCK-BIT CONFIGURATION POWER SUPPLY: For erasing array blocks, writing bytes or configuring block lock-bits. With V <sub>PP</sub> ≤V <sub>PPLK</sub> , memory contents cannot be altered. Block erase, full chip erase, (multi) word/byte write and block lock-bit configuration with an invalid V <sub>PP</sub> (see DC Characteristics) produce spurious results and should not be attempted.                                                                                                                                                                                                                                                                               |

| V <sub>CC</sub>                         | SUPPLY                  | <b>DEVICE POWER SUPPLY:</b> Internal detection configures the device for 5V operation. Do not float any power pins. With $V_{CC} \le V_{LKO}$ , all write attempts to the flash memory are inhibited. Device operations at invalid $V_{CC}$ voltage (see DC Characteristics) produce spurious results and should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                                         |

| GND                                     | SUPPLY                  | GROUND: Do not float any ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC                                      |                         | NO CONNECT: Lead is not internal connected; it may be driven or floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## 2 PRINCIPLES OF OPERATION

The LH28F160S5HNS-S1 Flash memory includes an on-chip WSM to manage block erase, full chip erase, (multi) word/byte write and block lock-bit configuration functions. It allows for: 100% TTL-level control inputs, fixed power supplies during block erase, full chip erase, (multi) word/byte write and block lock-bit configuration, and minimal processor overhead with RAM-Like interface timings.

After initial device power-up or return from deep power-down mode (see Bus Operations), the device defaults to read array mode. Manipulation of external memory control pins allow array read, standby, and output disable operations.

Status register, query structure and identifier codes can be accessed through the CUI independent of the  $V_{PP}$  voltage. High voltage on  $V_{PP}$  enables successful block erase, full chip erase, (multi) word/byte write and block lock-bit configuration. All functions associated with altering memory contents—block erase, full chip erase, (multi) word/byte write and block lock-bit configuration, status, query and identifier codes—are accessed via the CUI and verified through the status register.

Commands are written using standard microprocessor write timings. The CUI contents serve as input to the WSM, which controls the block erase, full chip erase, (multi) word/byte write and block lock-bit configuration. The internal algorithms are regulated by the WSM, including pulse repetition, internal verification, and margining of data. Addresses and data are internally latch during write cycles. Writing the appropriate command outputs array data, accesses the identifier codes, outputs query structure or outputs status register data.

Interface software that initiates and polls progress of block erase, full chip erase, (multi) word/byte write and block lock-bit configuration can be stored in any block. This code is copied to and executed from system RAM during flash memory updates. After successful completion, reads are again possible via the Read Array command. Block erase suspend allows system software to suspend a block erase to read or write data from any other block. Write suspend allows system software to suspend a (multi) word/byte write to read data from any other flash memory array location.

| 1FFFFF           |                |    |

|------------------|----------------|----|

| 1F0000           | 64K-byte Block | 31 |

| 1EFFFF<br>1E0000 | 64K-byte Block | 30 |

| 1DFFFF           | 64K-byte Block | 29 |

| 1CFFFF           | 64K-byte Block | 28 |

| 1C0000<br>1BFFFF | 64K-byte Block | 27 |

| 1B0000<br>1AFFFF | 64K-byte Block | 26 |

| 1A0000<br>19FFFF | 64K-byte Block | 25 |

| 190000<br>18FFFF | <u> </u>       | 24 |

| 180000<br>17FFFF | 64K-byte Block |    |

| 170000<br>16FFFF | 64K-byte Block | 23 |

| 160000<br>15FFFF | 64K-byte Block | 22 |

| 150000           | 64K-byte Block | 21 |

| 14FFFF<br>140000 | 64K-byte Block | 20 |

| 13FFFF<br>130000 | 64K-byte Block | 19 |

| 12FFFF<br>120000 | 64K-byte Block | 18 |

| 11FFFF<br>110000 | 64K-byte Block | 17 |

| 10FFFF           | 64K-byte Block | 16 |

| 100000<br>0FFFF  | 64K-byte Block | 15 |

| 0F0000<br>0EFFFF | 64K-byte Block | 14 |

| 0E0000<br>0DFFFF | 64K-byte Block | 13 |

| 0D0000<br>0CFFFF | 64K-byte Block | 12 |

| 0C0000<br>0BFFFF | 64K-byte Block | 11 |

| 0B0000<br>0AFFFF | 64K-byte Block | 10 |

| 0A0000<br>09FFFF | 64K-byte Block | 9  |

| 090000<br>08FFFF |                |    |

| 080000<br>07FFFF | 64K-byte Block | 8  |

| 070000<br>06FFFF | 64K-byte Block | 7  |

| 060000           | 64K-byte Block | 6  |

| 05FFFF<br>050000 | 64K-byte Block | 5  |

| 04FFFF<br>040000 | 64K-byte Block | 4  |

| 03FFFF<br>030000 | 64K-byte Block | 3  |

| 02FFFF<br>020000 | 64K-byte Block | 2  |

| 01FFFF           | 64K-byte Block | 1  |

| 010000<br>00FFFF | 64K-byte Block | 0  |

| 000000           | -              |    |

Figure 3. Memory Map

### 2.1 Data Protection

Depending on the application, the system designer may choose to make the  $V_{PP}$  power supply switchable (available only when block erase, full chip erase, (multi) word/byte write and block lock-bit configuration are required) or hardwired to  $V_{PPH1}$ . The device accommodates either design practice and encourages optimization of the processor-memory interface.

When  $V_{PP} \le V_{PPLK}$ , memory contents cannot be altered. The CUI, with multi-step block erase, full chip erase, (multi) word/byte write and block lock-bit configuration command sequences, provides protection from unwanted operations even when high voltage is applied to  $V_{PP}$ . All write functions are disabled when  $V_{CC}$  is below the write lockout voltage  $V_{LKO}$  or when RP# is at  $V_{IL}$ . The device's block locking capability provides additional protection from inadvertent code or data alteration by gating block erase, full chip erase and (multi) word/byte write operations.

### 3 BUS OPERATION

The local CPU reads and writes flash memory insystem. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.

### 3.1 Read

Information can be read from any block, identifier codes, query structure, or status register independent of the  $V_{PP}$  voltage. RP# must be at  $V_{IH}$ .

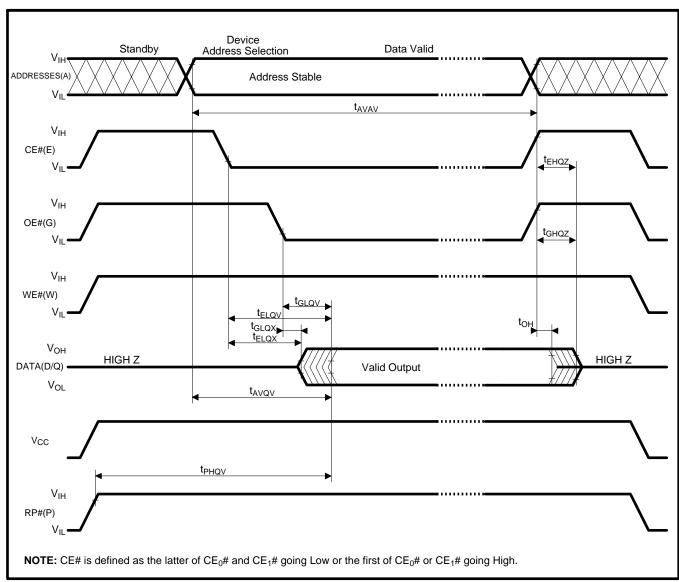

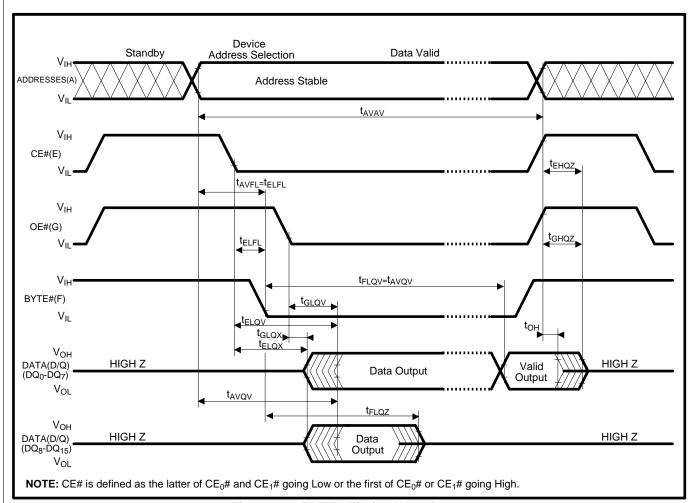

The first task is to write the appropriate read mode command (Read Array, Read Identifier Codes, Query or Read Status Register) to the CUI. Upon initial device power-up or after exit from deep power-down mode, the device automatically resets to read array mode. Five control pins dictate the data flow in and out of the component: CE# (CE $_0$ #, CE $_1$ #), OE#, WE#, RP# and WP#. CE $_0$ #, CE $_1$ # and OE# must be driven active to obtain data at the outputs. CE $_0$ #, CE $_1$ # is the device selection control, and when active enables the selected memory device. OE# is the data output (DQ $_0$ -DQ $_1$ 5) control and when active drives the selected memory data onto the I/O bus. WE# and RP# must be at V $_{IH}$ . Figure 17, 18 illustrates a read cycle.

## 3.2 Output Disable

With OE# at a logic-high level ( $V_{IH}$ ), the device outputs are disabled. Output pins DQ<sub>0</sub>-DQ<sub>15</sub> are placed in a high-impedance state.

## 3.3 Standby

Either CE<sub>0</sub># or CE<sub>1</sub># at a logic-high level (V<sub>IH</sub>) places the device in standby mode which substantially reduces device power consumption. DQ<sub>0</sub>-DQ<sub>15</sub> outputs are placed in a high-impedance state independent of OE#. If deselected during block erase, full chip erase, (multi) word/byte write and block lock-bit configuration, the device continues functioning, and consuming active power until the operation completes.

## 3.4 Deep Power-Down

RP# at  $V_{II}$  initiates the deep power-down mode.

In read modes, RP#-low deselects the memory, places output drivers in a high-impedance state and turns off all internal circuits. RP# must be held low for a minimum of 100 ns. Time t<sub>PHQV</sub> is required after return from power-down until initial memory access outputs are valid. After this wake-up interval, normal operation is restored. The CUI is reset to read array mode and status register is set to 80H.

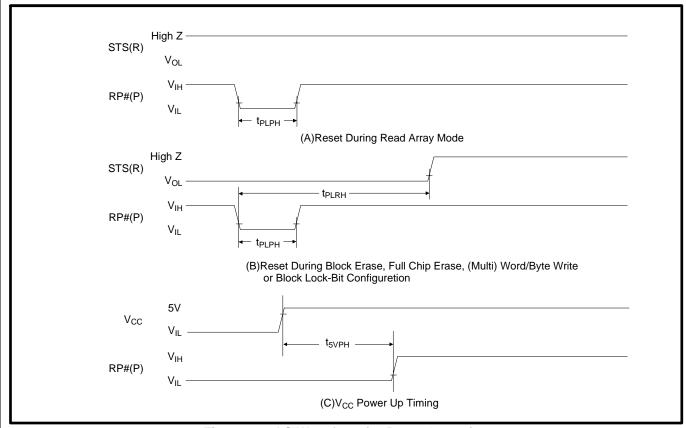

During block erase, full chip erase, (multi) word/byte write or block lock-bit configuration modes, RP#-low will abort the operation. STS remains low until the reset operation is complete. Memory contents being altered are no longer valid; the data may be partially erased or written. Time  $t_{\rm PHWL}$  is required after RP# goes to logic-high (V $_{\rm IH}$ ) before another command can be written.

As with any automated device, it is important to assert RP# during system reset. When the system comes out of reset, it expects to read from the flash memory. Automated flash memories provide status information when accessed during block erase, full chip erase, (multi) word/byte write and block lock-bit configuration. If a CPU reset occurs with no flash memory reset, proper CPU initialization may not occur because the flash memory may be providing status information instead of array data. SHARP's flash memories allow proper CPU initialization following a system reset through the use of the RP# input. In this application, RP# is controlled by the same RESET# signal that resets the system CPU.

## 3.5 Read Identifier Codes Operation

The read identifier codes operation outputs the manufacturer code, device code, block status codes for each block (see Figure 4). Using the manufacturer and device codes, the system CPU can automatically match the device with its proper algorithms. The block status codes identify locked or unlocked block setting and erase completed or erase uncompleted condition.

Figure 4. Device Identifier Code Memory Map

## 3.6 Query Operation

The query operation outputs the query structure. Query database is stored in the 48Byte ROM. Query structure allows system software to gain critical information for controlling the flash component. Query structure are always presented on the lowest-order data output  $(DQ_0-DQ_7)$  only.

#### 3.7 Write

Writing commands to the CUI enable reading of device data and identifier codes. They also control inspection and clearing of the status register. When  $V_{CC}=V_{CC1/2}$  and  $V_{PP}=V_{PPH1}$ , the CUI additionally controls block erase, full chip erase, (multi) word/byte write and block lock-bit configuration.

The Block Erase command requires appropriate command data and an address within the block to be erased. The Word/byte Write command requires the command and address of the location to be written. Set Block Lock-Bit command requires the command and block address within the device (Block Lock) to be locked. The Clear Block Lock-Bits command requires the command and address within the device.

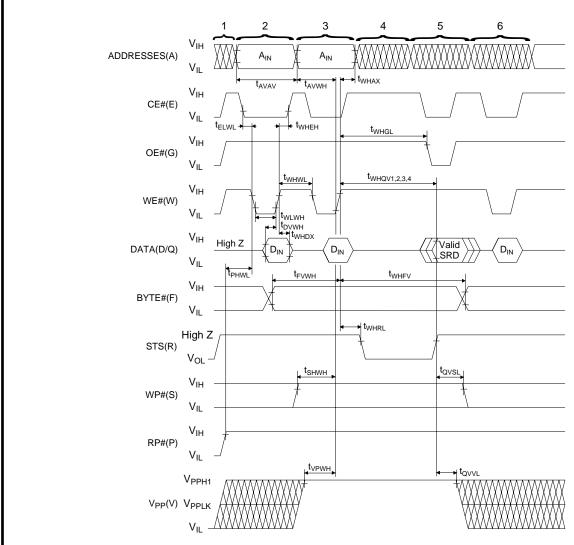

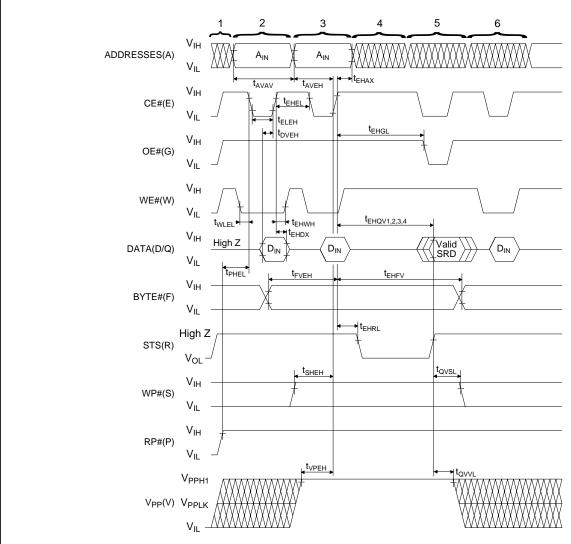

The CUI does not occupy an addressable memory location. It is written when WE# and CE# are active. The address and data needed to execute a command are latched on the rising edge of WE# or CE# (whichever goes high first). Standard microprocessor write timings are used. Figures 19 and 20 illustrate WE# and CE#-controlled write operations.

#### 4 COMMAND DEFINITIONS

When the  $V_{PP}$  voltage  $\leq V_{PPLK}$ , Read operations from the status register, identifier codes, query, or blocks are enabled. Placing  $V_{PPH1}$  on  $V_{PP}$  enables successful block erase, full chip erase, (multi) word/byte write and block lock-bit configuration operations.

Device operations are selected by writing specific commands into the CUI. Table 4 defines these commands.

Table 3. Bus Operations(BYTE#=V...)

|                          |         | ıu              | DIC J. D                                              | us Opcit                                              | 1110113(15      | L               | H <i>)</i>      |                 |                    |        |

|--------------------------|---------|-----------------|-------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|--------------------|--------|

| Mode                     | Notes   | RP#             | CE <sub>0</sub> #                                     | CE <sub>1</sub> #                                     | OE#             | WE#             | Address         | V <sub>PP</sub> | DQ <sub>0-15</sub> | STS    |

| Read                     | 1,2,3,9 | $V_{IH}$        | VII                                                   | VII                                                   | V <sub>II</sub> | $V_{IH}$        | X               | X               | D <sub>OUT</sub>   | Х      |

| Output Disable           | 3       | V <sub>IH</sub> | Vii                                                   | Vil                                                   | V <sub>IH</sub> | V <sub>IH</sub> | X               | Х               | High Z             | Х      |

| Standby                  | 3       | V <sub>IH</sub> | V <sub>IH</sub><br>V <sub>IH</sub><br>V <sub>II</sub> | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>IH</sub> | X               | X               | x               | X               | High Z             | х      |

| Deep Power-Down          | 4       | V <sub>IL</sub> | X                                                     | X                                                     | Х               | Х               | X               | Х               | High Z             | High Z |

| Read Identifier<br>Codes | 9       | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Figure 4 | Х               | Note 5             | High Z |

| Query                    | 9       | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IL</sub> | V <sub>IH</sub> | See Table 7~11  | Х               | Note 6             | High Z |

| Write                    | 3,7,8,9 | $V_{IH}$        | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IH</sub> | V <sub>IL</sub> | X               | Χ               | D <sub>IN</sub>    | Х      |

Table 3.1. Bus Operations(BYTE#=V<sub>11</sub>)

|                          |         |                 |                                                       | ouc opc.                                              | ~               | · · · <b>—</b>  | IL/               |          |                   |        |

|--------------------------|---------|-----------------|-------------------------------------------------------|-------------------------------------------------------|-----------------|-----------------|-------------------|----------|-------------------|--------|

| Mode                     | Notes   | RP#             | CE <sub>0</sub> #                                     | CE <sub>1</sub> #                                     | OE#             | WE#             | Address           | $V_{PP}$ | DQ <sub>0-7</sub> | STS    |

| Read                     | 1,2,3,9 | $V_{IH}$        | VII                                                   | VII                                                   | V <sub>II</sub> | V <sub>IH</sub> | X                 | Χ        | D <sub>OUT</sub>  | X      |

| Output Disable           | 3       | V <sub>IH</sub> | V <sub>II</sub>                                       | V <sub>II</sub>                                       | V <sub>IH</sub> | V <sub>IH</sub> | X                 | Χ        | High Z            | X      |

| Standby                  | 3       | V <sub>IH</sub> | V <sub>IH</sub><br>V <sub>IH</sub><br>V <sub>II</sub> | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>IH</sub> | X               | X               | X                 | Х        | High Z            | Х      |

| Deep Power-Down          | 4       | V <sub>II</sub> | X                                                     | X                                                     | Х               | Х               | X                 | Х        | High Z            | High Z |

| Read Identifier<br>Codes | 9       | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Figure 4   | Х        | Note 5            | High Z |

| Query                    | 9       | V <sub>IH</sub> | V <sub>IL</sub>                                       | V <sub>IL</sub>                                       | V <sub>IL</sub> | V <sub>IH</sub> | See Table<br>7~11 | Х        | Note 6            | High Z |

| Write                    | 3,7,8,9 | $V_{IH}$        | V <sub>IL</sub>                                       | $V_{IL}$                                              | V <sub>IH</sub> | V <sub>IL</sub> | X                 | Χ        | D <sub>IN</sub>   | Х      |

#### **NOTES:**

- Refer to DC Characteristics. When V<sub>PP</sub>≤V<sub>PPLK</sub>, memory contents can be read, but not altered.

X can be V<sub>IL</sub> or V<sub>IH</sub> for control pins and addresses, and V<sub>PPLK</sub> or V<sub>PPLH</sub> for V<sub>PP</sub>. See DC Characteristics for V<sub>PPLK</sub> and V<sub>PPH1</sub> voltages.

- 3. STS is V<sub>OI</sub> (if configured to RY/BY# mode) when the WSM is executing internal block erase, full chip erase, (multi) word/byte write or block lock-bit configuration algorithms. It is floated during when the WSM is not busy, in block erase suspend mode with (multi) word/byte write inactive, (multi) word/byte write suspend mode, or deep power-down mode.

- 4. RP# at GND±0.2V ensures the lowest deep power-down current.

- 5. See Section 4.2 for read identifier code data.

- 6. See Section 4.5 for query data.

- 7. Command writes involving block erase, full chip erase, (multi) word/byte write or block lock-bit configuration are reliably executed when  $V_{PP}=V_{PPH1}$  and  $V_{CC}=V_{CC1/2}$ . 8. Refer to Table 4 for valid  $D_{IN}$  during a write operation. 9. Don't use the timing both OE# and WE# are  $V_{IL}$ .

| Table 4. Command Definitions <sup>(10)</sup>                         |                   |       |                     |                     |                     |                     |                     |                     |

|----------------------------------------------------------------------|-------------------|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|                                                                      | <b>Bus Cycles</b> | Notes |                     | st Bus Cy           |                     |                     | ond Bus C           | ycle                |

| Command                                                              | Req'd             |       | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data <sup>(3)</sup> | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data <sup>(3)</sup> |

| Read Array/Reset                                                     | 1                 |       | Write               | Х                   | FFH                 |                     |                     |                     |

| Read Identifier Codes                                                | ≥2                | 4     | Write               | Х                   | 90H                 | Read                | IA                  | ID                  |

| Query                                                                | ≥2                |       | Write               | Х                   | 98H                 | Read                | QA                  | QD                  |

| Read Status Register                                                 | 2                 |       | Write               | Х                   | 70H                 | Read                | Х                   | SRD                 |

| Clear Status Register                                                | 1                 |       | Write               | Х                   | 50H                 |                     |                     |                     |

| Block Erase Setup/Confirm                                            | 2                 | 5     | Write               | BA                  | 20H                 | Write               | BA                  | D0H                 |

| Full Chip Erase Setup/Confirm                                        | 2                 |       | Write               | X                   | 30H                 | Write               | Χ                   | D0H                 |

| Word/Byte Write Setup/Write                                          | 2                 | 5,6   | Write               | WA                  | 40H                 | Write               | WA                  | WD                  |

| Alternate Word/Byte Write Setup/Write                                | 2                 | 5,6   | Write               | WA                  | 10H                 | Write               | WA                  | WD                  |

| Multi Word/Byte Write<br>Setup/Confirm                               | ≥4                | 9     | Write               | WA                  | E8H                 | Write               | WA                  | N-1                 |

| Block Erase and (Multi) Word/byte Write Suspend                      | 1                 | 5     | Write               | Х                   | ВОН                 |                     |                     |                     |

| Confirm and Block Erase and (Multi) Word/byte Write Resume           | 1                 | 5     | Write               | Х                   | D0H                 |                     |                     |                     |

| Block Lock-Bit Set Setup/Confirm                                     | 2                 | 7     | Write               | BA                  | 60H                 | Write               | BA                  | 01H                 |

| Block Lock-Bit Reset<br>Setup/Confirm                                | 2                 | 8     | Write               | Х                   | 60H                 | Write               | Х                   | D0H                 |

| STS Configuration<br>Level-Mode for Erase and Write<br>(RY/BY# Mode) | 2                 |       | Write               | Х                   | B8H                 | Write               | Х                   | 00H                 |

| STS Configuration Pulse-Mode for Erase                               | 2                 |       | Write               | Х                   | В8Н                 | Write               | Х                   | 01H                 |

| STS Configuration Pulse-Mode for Write                               | 2                 |       | Write               | Х                   | B8H                 | Write               | Х                   | 02H                 |

| STS Configuration Pulse-Mode for Erase and Write                     | 2                 |       | Write               | Х                   | В8Н                 | Write               | Х                   | 03H                 |

#### NOTES:

- 1. BUS operations are defined in Table 3 and Table 3.1.

- 2. X=Any valid address within the device.

IA=Identifier Code Address: see Figure 4.

QA=Query Offset Address.

BA=Address within the block being erased or locked.

WA=Address of memory location to be written.

- 3. SRD=Data read from status register. See Table 14 for a description of the status register bits.

- WD=Data to be written at location WA. Data is latched on the rising edge of WE# or CE# (whichever goes high first).

- ID=Data read from identifier codes.

- QD=Data read from query database.

- 4. Following the Read Identifier Codes command, read operations access manufacturer, device and block status codes. See Section 4.2 for read identifier code data.

- 5. If the block is locked, WP# must be at  $V_{IH}$  to enable block erase or (multi) word/byte write operations. Attempts to issue a block erase or (multi) word/byte write to a locked block while RP# is  $V_{IH}$ .

- 6. Either 40H or 10H are recognized by the WSM as the byte write setup.

- 7. A block lock-bit can be set while WP# is  $V_{IH}$ .

- 8. WP# must be at V<sub>IH</sub> to clear block lock-bits. The clear block lock-bits operation simultaneously clears all block lock-bits.

- 9. Following the Third Bus Cycle, inputs the write address and write data of 'N' times. Finally, input the confirm command 'D0H'.

- 10. Commands other than those shown above are reserved by SHARP for future device implementations and should not be used.

## 4.1 Read Array Command

Upon initial device power-up and after exit from deep power-down mode, the device defaults to read array mode. This operation is also initiated by writing the Read Array command. The device remains enabled for reads until another command is written. Once the internal WSM has started a block erase, full chip erase, (multi) word/byte write or block lock-bit configuration, the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via an Erase Suspend and (Multi) Word/byte Write Suspend command. The Read Array command functions independently of the  $\rm V_{PP}$  voltage and RP# must be  $\rm V_{IH}$ .

## 4.2 Read Identifier Codes Command

The identifier code operation is initiated by writing the Read Identifier Codes command. Following the command write, read cycles from addresses shown in Figure 4 retrieve the manufacturer, device, block lock configuration and block erase status (see Table 5 for identifier code values). To terminate the operation, write another valid command. Like the Read Array command, the Read Identifier Codes command functions independently of the  $V_{PP}$  voltage and RP# must be  $V_{IH}$ . Following the Read Identifier Codes command, the following information can be read:

**Table 5. Identifier Codes**

| 10.0010 01 10.01111                          |                      |                    |

|----------------------------------------------|----------------------|--------------------|

| Code                                         | Address              | Data               |

| Manufacture Code                             | 00000                | В0                 |

|                                              | 00001<br>00002       |                    |

| Device Code                                  | 00003                | D0                 |

| Block Status Code                            | X0004 <sup>(1)</sup> |                    |

|                                              | X0005 <sup>(1)</sup> |                    |

| Block is Unlocked                            |                      | $DQ_0=0$           |

| Block is Locked                              |                      | DQ <sub>0</sub> =1 |

| Last erase operation                         |                      | DQ <sub>1</sub> =0 |

| completed successfully                       |                      | 2410               |

| <ul> <li>Last erase operation did</li> </ul> |                      | DQ <sub>1</sub> =1 |

| not completed successfully                   |                      | D 9 1 - 1          |

| <ul> <li>Reserved for Future Use</li> </ul>  |                      | DQ <sub>2-7</sub>  |

#### NOTE:

X selects the specific block status code to be read. See Figure 4 for the device identifier code memory map.

## 4.3 Read Status Register Command

The status register may be read to determine when a block erase, full chip erase, (multi) word/byte write or block lock-bit configuration is complete and whether the operation completed successfully(see Table 14). It may be read at any time by writing the Read Status Register command. After writing this command, all subsequent read operations output data from the status register until another valid command is written. The status register contents are latched on the falling edge of OE# or CE#(Either CE $_0$ # or CE $_1$ #), whichever occurs. OE# or CE#(Either CE $_0$ # or CE $_1$ #) must toggle to V $_{\rm IH}$  before further reads to update the status register latch. The Read Status Register command functions independently of the V $_{\rm PP}$  voltage. RP# must be V $_{\rm IH}$ .

The extended status register may be read to determine multi word/byte write availability(see Table 14.1). The extended status register may be read at any time by writing the Multi Word/Byte Write command. After writing this command, all subsequent read operations output data from the extended status register, until another valid command is written. Multi Word/Byte Write command must be re-issued to update the extended status register latch.

## 4.4 Clear Status Register Command

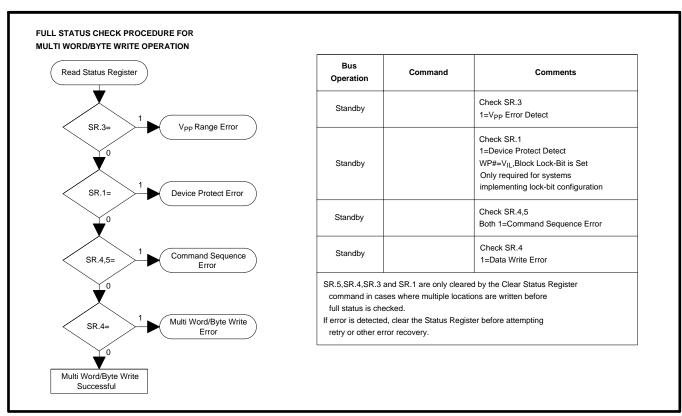

Status register bits SR.5, SR.4, SR.3 and SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 14). By allowing system software to reset these bits, several operations (such as cumulatively erasing or locking multiple blocks or writing several bytes in sequence) may be performed. The status register may be polled to determine if an error occurs during the sequence.

To clear the status register, the Clear Status Register command (50H) is written. It functions independently of the applied  $V_{PP}$  Voltage. RP# must be  $V_{IH}$ . This command is not functional during block erase, full chip erase, (multi) word/byte write block lock-bit configuration, block erase suspend or (multi) word/byte write suspend modes.

## 4.5 Query Command

Query database can be read by writing Query command (98H). Following the command write, read cycle from address shown in Table 7~11 retrieve the critical information to write, erase and otherwise control the flash component.  $A_0$  of query offset address is ignored when X8 mode (BYTE#= $V_{\rm IL}$ ).

Query data are always presented on the low-byte data output ( $DQ_0$ - $DQ_7$ ). In x16 mode, high-byte ( $DQ_8$ - $DQ_{15}$ ) outputs 00H. The bytes not assigned to any information or reserved for future use are set to "0". This command functions independently of the  $V_{PP}$  voltage. RP# must be  $V_{IH}$ .

| rable 6. Example of Query Structure Output |                                                                                                                                                                                                                |                            |                          |  |  |  |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------|--|--|--|--|--|

| Mode                                       | Offset Address                                                                                                                                                                                                 | Output                     |                          |  |  |  |  |  |

|                                            |                                                                                                                                                                                                                | DQ <sub>15~8</sub>         | DQ <sub>7~0</sub>        |  |  |  |  |  |

| X8 mode                                    | A <sub>5</sub> , A <sub>4</sub> , A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub> , A <sub>0</sub><br>1, 0, 0, 0, 0, 0, 0 (20H)<br>1, 0, 0, 0, 0, 1 (21H)<br>1, 0, 0, 0, 1, 0 (22H)<br>1, 0, 0, 0, 1, 1 (23H) | High Z<br>High Z<br>High Z | "Q"<br>"Q"<br>"R"<br>"R" |  |  |  |  |  |

| X16 mode                                   | A <sub>5</sub> , A <sub>4</sub> , A <sub>3</sub> , A <sub>2</sub> , A <sub>1</sub><br>1, 0, 0, 0, 0 (10H)<br>1, 0, 0, 0, 1 (11H)                                                                               | 00H<br>00H                 | "Q"<br>"R"               |  |  |  |  |  |

Table 6 Example of Query Structure Quinut

## 4.5.1 Block Status Register

This field provides lock configuration and erase status for the specified block. These informations are only available when device is ready (SR.7=1). If block erase or full chip erase operation is finished irregulary, block erase status bit will be set to "1". If bit 1 is "1", this block is invalid.

Table 7. Query Block Status Register

| Offset<br>(Word Address) | Length | Description                                                                                                                                                                                                                                      |  |

|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (BA+2)H                  | 01H    | Block Status Register bit0 Block Lock Configuration 0=Block is unlocked 1=Block is Locked bit1 Block Erase Status 0=Last erase operation completed successfully 1=Last erase operation not completed successfully bit2-7 reserved for future use |  |

#### Note:

1. BA=The beginning of a Block Address.

## 4.5.2 CFI Query Identification String

The Identification String provides verification that the component supports the Common Flash Interface specification. Additionally, it indicates which version of the spec and which Vendor-specified command set(s) is(are) supported.

Table 8. CFI Query Identification String

| Offset<br>(Word Address) | Length | Description                                                                                             |  |

|--------------------------|--------|---------------------------------------------------------------------------------------------------------|--|

| 10H,11H,12H              | 03H    | Query Unique ASCII string "QRY" 51H,52H,59H                                                             |  |

| 13H,14H                  | 02H    | rimary Vendor Command Set and Control Interface ID Code 1H,00H (SCS ID Code)                            |  |

| 15H,16H                  | 02H    | ddress for Primary Algorithm Extended Query Table 1H,00H (SCS Extended Query Table Offset)              |  |

| 17H,18H                  | 02H    | Alternate Vendor Command Set and Control Interface ID Code 0000H (0000H means that no alternate exists) |  |

| 19H,1AH                  | 02H    | Address for Alternate Algorithm Extended Query Table 0000H (0000H means that no alternate exists)       |  |

## 4.5.3 System Interface Information

The following device information can be useful in optimizing system interface software.

**Table 9. System Information String**

| Table 9. System Information String |        |                                                                                                                          |  |  |

|------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Offset<br>(Word Address)           | Length | Description                                                                                                              |  |  |

| 1BH                                | 01H    | V <sub>CC</sub> Logic Supply Minimum Write/Erase voltage 27H (2.7V)                                                      |  |  |

| 1CH                                | 01H    | V <sub>CC</sub> Logic Supply Maximum Write/Erase voltage 55H (5.5V)                                                      |  |  |

| 1DH                                | 01H    | V <sub>PP</sub> Programming Supply Minimum Write/Erase voltage 27H (2.7V)                                                |  |  |

| 1EH                                | 01H    | V <sub>PP</sub> Programming Supply Maximum Write/Erase voltage 55H (5.5V)                                                |  |  |

| 1FH                                | 01H    | Typical Timeout per Single Byte/Word Write 03H (2 <sup>3</sup> =8µs)                                                     |  |  |

| 20H                                | 01H    | ypical Timeout for Maximum Size Buffer Write (32 Bytes)<br>6H (2 <sup>6</sup> =64µs)                                     |  |  |

| 21H                                | 01H    | Typical Timeout per Individual Block Erase 0AH (0AH=10, 2 <sup>10</sup> =1024ms)                                         |  |  |

| 22H                                | 01H    | Typical Timeout for Full Chip Erase<br>0FH (0FH=15, 2 <sup>15</sup> =32768ms)                                            |  |  |

| 23H                                | 01H    | Maximum Timeout per Single Byte/Word Write, 2 <sup>N</sup> times of typical. 04H (2 <sup>4</sup> =16, 8µsx16=128µs)      |  |  |

| 24H                                | 01H    | Maximum Timeout Maximum Size Buffer Write, 2 <sup>N</sup> times of typical. 04H (2 <sup>4</sup> =16, 64µsx16=1024µs)     |  |  |

| 25H                                | 01H    | Maximum Timeout per Individual Block Erase, 2 <sup>N</sup> times of typical. 04H (2 <sup>4</sup> =16, 1024msx16=16384ms) |  |  |

| 26H                                | 01H    | Maximum Timeout for Full Chip Erase, 2 <sup>N</sup> times of typical.  04H (2 <sup>4</sup> =16, 32768msx16=524288ms)     |  |  |

## 4.5.4 Device Geometry Definition

This field provides critical details of the flash device geometry.

**Table 10. Device Geometry Definition**

| Offset<br>(Word Address) | Length | Description                                                        |  |

|--------------------------|--------|--------------------------------------------------------------------|--|

| 27H                      | 01H    | Device Size                                                        |  |

|                          |        | 15H (15H=21, 2 <sup>21</sup> =2097152=2M Bytes)                    |  |

| 28H,29H                  | 02H    | Flash Device Interface description                                 |  |

|                          |        | 02H,00H (x8/x16 supports x8 and x16 via BYTE#)                     |  |

| 2AH,2BH                  | 02H    | Maximum Number of Bytes in Multi word/byte write                   |  |

|                          |        | 05H,00H (2 <sup>5</sup> =32 Bytes )                                |  |

| 2CH                      | 01H    | Number of Erase Block Regions within device                        |  |

|                          |        | 01H (symmetrically blocked)                                        |  |

| 2DH,2EH                  | 02H    | The Number of Erase Blocks                                         |  |

|                          |        | 1FH,00H (1FH=31 ==> 31+1=32 Blocks)                                |  |

| 2FH,30H                  | 02H    | The Number of "256 Bytes" cluster in a Erase block                 |  |

|                          |        | 00H,01H (0100H=256 ==>256 Bytes x 256= 64K Bytes in a Erase Block) |  |

## 4.5.5 SCS OEM Specific Extended Query Table

Certain flash features and commands may be optional in a vendor-specific algorithm specification. The optional vendor-specific Query table(s) may be used to specify this and other types of information. These structures are defined solely by the flash vendor(s).

Table 11. SCS OEM Specific Extended Query Table

|                          | iak      | ne 11. 303 OLIN Specific Extended Query Table                                                 |  |

|--------------------------|----------|-----------------------------------------------------------------------------------------------|--|

| Offset<br>(Word Address) | Length   | Description                                                                                   |  |

| 31H,32H,33H              | 03H      | PRI                                                                                           |  |

|                          |          | 50H,52H,49H                                                                                   |  |

| 34H                      | 01H      | 31H (1) Major Version Number , ASCII                                                          |  |

| 35H                      | 01H      | 30H (0) Minor Version Number, ASCII                                                           |  |

| 36H,37H,                 | 04H      | 0FH,00H,00H                                                                                   |  |

| 38H,39H                  |          | Optional Command Support                                                                      |  |

|                          |          | bit0=1 : Chip Erase Supported                                                                 |  |

|                          |          | bit1=1 : Suspend Erase Supported                                                              |  |

|                          |          | bit2=1 : Suspend Write Supported                                                              |  |

|                          |          | bit3=1 : Lock/Unlock Supported                                                                |  |

|                          |          | bit4=0 : Queued Erase Not Supported                                                           |  |

|                          |          | bit5-31=0 : reserved for future use                                                           |  |

| 3AH                      | 01H      | 01H                                                                                           |  |

|                          |          | Supported Functions after Suspend                                                             |  |

|                          |          | bit0=1: Write Supported after Erase Suspend                                                   |  |

|                          |          | bit1-7=0 : reserved for future use                                                            |  |

| 3BH,3CH                  | 02H      | 03H,00H                                                                                       |  |

|                          |          | Block Status Register Mask                                                                    |  |

|                          |          | bit0=1 : Block Status Register Lock Bit [BSR.0] active                                        |  |

|                          |          | bit1=1 : Block Status Register Valid Bit [BSR.1] active                                       |  |

|                          |          | bit2-15=0 : reserved for future use                                                           |  |

| 3DH                      | 01H      | V <sub>CC</sub> Logic Supply Optimum Write/Erase voltage(highest performance)                 |  |

|                          |          | 50H(5.0V)                                                                                     |  |

| 3EH                      | 01H      | V <sub>PP</sub> Programming Supply Optimum Write/Erase voltage(highest performance) 50H(5.0V) |  |

| 3FH                      | reserved | Reserved for future versions of the SCS Specification                                         |  |

## 4.6 Block Erase Command

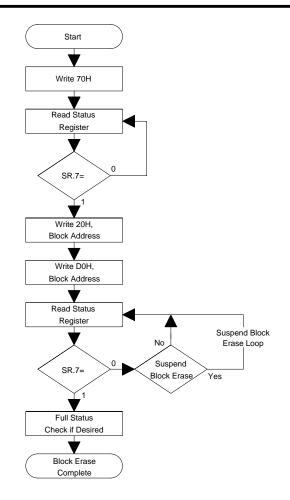

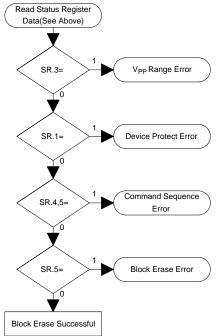

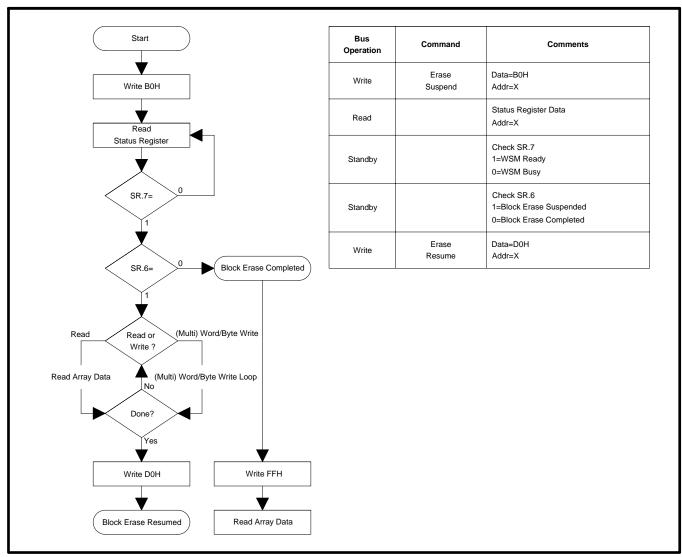

Block erase is executed one block at a time and initiated by a two-cycle command. A block erase setup is first written, followed by an block erase confirm. This command sequence appropriate sequencing and an address within the block to be erased (erase changes all block data to FFH). Block preconditioning, erase and verify are handled internally by the WSM (invisible to the system). After the two-cycle block erase sequence is written, the device automatically outputs status register data when read (see Figure 5). The CPU can detect block erase completion by analyzing the output data of the STS pin or status register bit SR.7.

When the block erase is complete, status register bit SR.5 should be checked. If a block erase error is detected, the status register should be cleared before system software attempts corrective actions. The CUI remains in read status register mode until a new command is issued.

This two-step command sequence of set-up followed by execution ensures that block contents are not accidentally erased. An invalid Block Erase command sequence will result in both status register bits SR.4 and SR.5 being set to "1". Also, reliable block erasure can only occur when  $V_{CC}=V_{CC1/2}$  and  $V_{PP}=V_{PPH1}$ . In the absence of this high voltage, block contents are protected against erasure. If block erase is attempted while  $V_{PP}\leq V_{PPLK}$ , SR.3 and SR.5 will be set to "1". Successful block erase requires that the corresponding block lock-bit be cleared or if set, that WP#= $V_{IH}$ . If block erase is attempted when the corresponding block lock-bit is set and WP#= $V_{IL}$ , SR.1 and SR.5 will be set to "1".

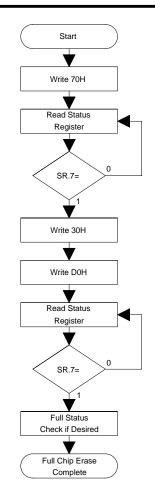

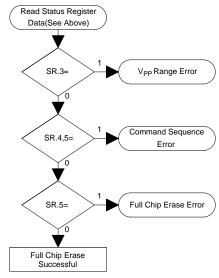

## 4.7 Full Chip Erase Command

This command followed by a confirm command (D0H) erases all of the unlocked blocks. A full chip

erase setup is first written, followed by a full chip erase confirm. After a confirm command is written, device erases the all unlocked blocks from block 0 to Block 31 block by block. This command sequence requires appropriate sequencing. Block preconditioning, erase and verify are handled internally by the WSM (invisible to the system). After the two-cycle full chip erase sequence is written, the device automatically outputs status register data when read (see Figure 6). The CPU can detect full chip erase completion by analyzing the output data of the STS pin or status register bit SR.7.

When the full chip erase is complete, status register bit SR.5 should be checked. If erase error is detected, the status register should be cleared before system software attempts corrective actions. The CUI remains in read status register mode until a new command is issued. If error is detected on a block during full chip erase operation, WSM stops erasing. Reading the block valid status by issuing Read ID Codes command or Query command informs which blocks failed to its erase.

This two-step command sequence of set-up followed by execution ensures that block contents are not accidentally erased. An invalid Full Chip Erase command sequence will result in both status register bits SR.4 and SR.5 being set to "1". Also, reliable full chip erasure can only occur when  $V_{CC} = V_{CC1/2}$  and  $V_{PP} = V_{PPH1}$ . In the absence of this high voltage, block contents are protected against erasure. If full chip erase is attempted while  $V_{PP} {\leq} V_{PPLK}$ , SR.3 and SR.5 will be set to "1". When WP#= $V_{IH}$ , all blocks are erased independent of block lock-bits status. When WP#= $V_{IL}$ , only unlocked blocks are erased. In this case, SR.1 and SR.5 will not be set to "1". Full chip erase can not be suspended.

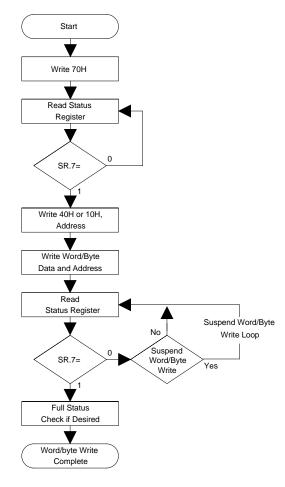

## 4.8 Word/Byte Write Command

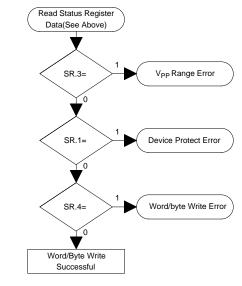

Word/byte write is executed by a two-cycle command sequence. Word/Byte Write setup (standard 40H or alternate 10H) is written, followed by a second write that specifies the address and data (latched on the rising edge of WE#). The WSM then takes over, controlling the word/byte write and write verify algorithms internally. After the word/byte write sequence is written, the device automatically outputs status register data when read (see Figure 7). The CPU can detect the completion of the word/byte write event by analyzing the STS pin or status register bit SR.7.

When word/byte write is complete, status register bit SR.4 should be checked. If word/byte write error is detected, the status register should be cleared. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s. The CUI remains in read status register mode until it receives another command.

Reliable word/byte writes can only occur when  $V_{CC}=V_{CC1/2}$  and  $V_{PP}=V_{PPH1}$ . In the absence of this high voltage, memory contents are protected against word/byte writes. If word/byte write is attempted while  $V_{PP} \le V_{PPLK}$ , status register bits SR.3 and SR.4 will be set to "1". Successful word/byte write requires that the corresponding block lock-bit be cleared or, if set, that WP#= $V_{IH}$ . If word/byte write is attempted when the corresponding block lock-bit is set and WP#= $V_{IL}$ , SR.1 and SR.4 will be set to "1". Word/byte write operations with  $V_{IL} < WP\# < V_{IH}$  produce spurious results and should not be attempted.

## 4.9 Multi Word/Byte Write Command

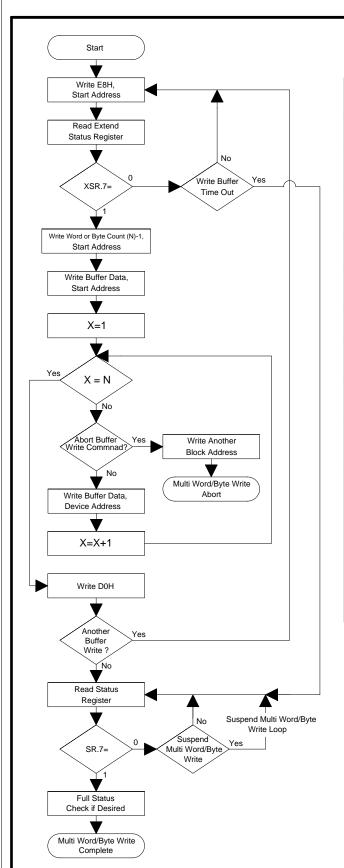

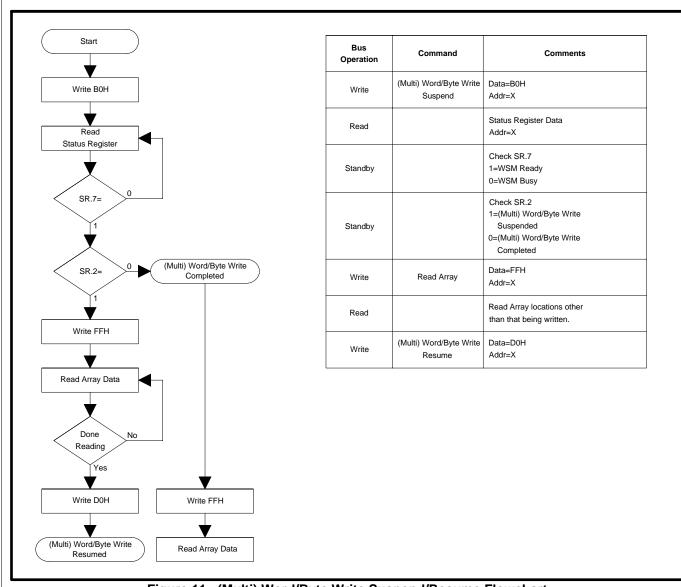

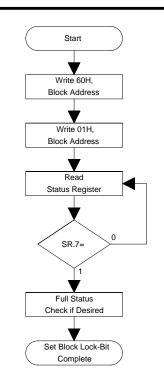

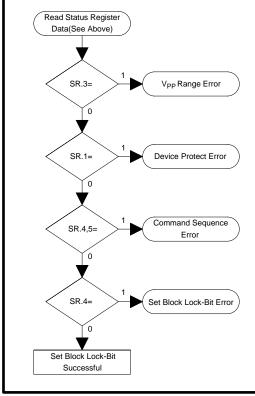

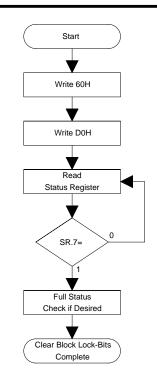

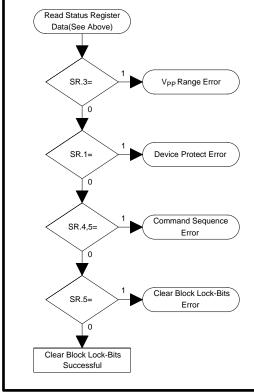

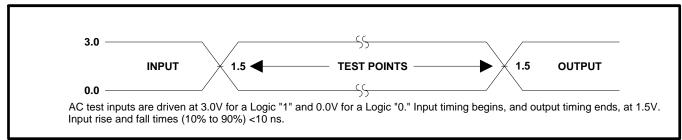

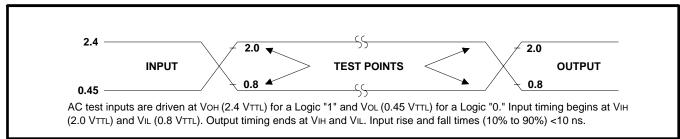

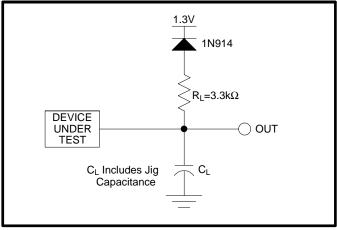

Multi word/byte write is executed by at least four-cycle or up to 35-cycle command sequence. Up to 32 bytes in x8 mode (16 words in x16 mode) can be loaded into the buffer and written to the Flash Array. First, multi word/byte write setup (E8H) is written with the write address. At this point, the device automatically outputs extended status register data (XSR) when read (see Figure 8, 9). If extended status register bit XSR.7 is 0, no Multi Word/Byte Write command is available and multi word/byte write setup which just has been written is ignored. To retry,